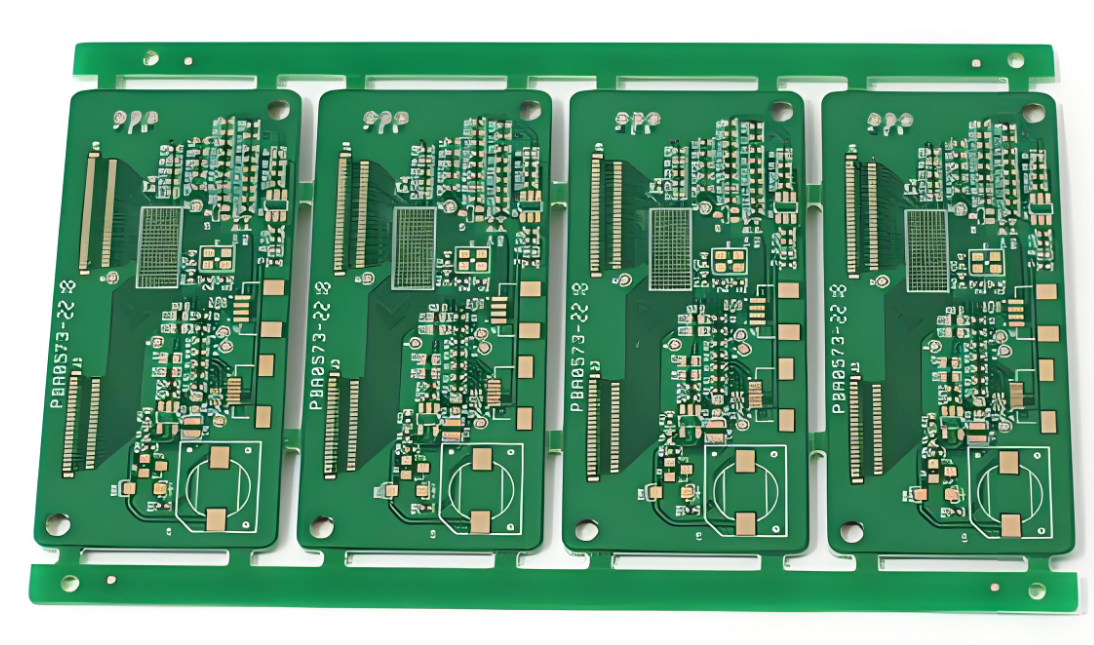

很多电子工程师在PCB打样时经常遇到莫名加价、交期延误、品质不合格等问题,其实大部分情况都是前期没注意细节导致的。了解常见的打样坑点,提前规避,既能省钱,又能保证项目顺利推进。

首先是尺寸超规格导致价格翻倍。大部分平台的低价和免费打样都限定在10cm×10cm以内以及5cmx5cm内,很多工程师设计时稍微超出一点,价格就立刻上涨,这是最常见也最容易避免的问题。设计阶段提前确认尺寸,就能省下不少成本。

其次是工艺选择不当。普通打样选择喷锡即可,性价比最高。如果随意选择沉金、镀金、厚铜等特殊工艺,价格会高出很多,对于普通研发打样完全没有必要。只有高频、高可靠需求的产品,才需要特殊表面处理。

第三是Gerber文件不规范。文件缺失、线路错误、孔径不标准,都会导致厂家无法生产或要求修改,耽误交期。提交前简单自查,保证文件完整,能大幅减少返工和沟通成本。

第四是盲目选择加急。加急打样价格通常是普通交期的几倍,大部分研发项目并不需要24小时加急。合理规划项目进度,选择标准交期,能省下一大笔费用。

第五是忽略厂家规则。嘉立创、华秋、捷配、捷多邦等平台都有自己的工艺规范和优惠限制,不看规则直接下单,很容易导致订单被拒或额外收费。熟悉规则,才能真正做到省钱省心。

PCB打样虽然环节简单,但细节直接影响价格和进度。对于电子工程师来说,提前避坑、规范设计、合理选择工艺和交期,才能用最低成本做出合格的样板。